ઇલેક્ટ્રીક કેપેસીટન્સ એ ઇલેકટ્રોસ્ટેટીક્સની મૂળભૂત વિભાવનાઓમાંની એક છે. આ શબ્દ ઇલેક્ટ્રિક ચાર્જ એકઠા કરવાની ક્ષમતાનો સંદર્ભ આપે છે. તમે અલગ વાહકની ક્ષમતા વિશે વાત કરી શકો છો, તમે બે અથવા વધુ વાહકની સિસ્ટમની ક્ષમતા વિશે વાત કરી શકો છો. શારીરિક પ્રક્રિયાઓ સમાન છે.

સામગ્રી

વિદ્યુત ક્ષમતા સંબંધિત મૂળભૂત ખ્યાલો

જો વાહકને ચાર્જ q મળ્યો હોય, તો તેના પર સંભવિત φ ઉદ્ભવે છે. આ સંભવિત ભૂમિતિ અને પર્યાવરણ પર આધાર રાખે છે - વિવિધ વાહક અને પરિસ્થિતિઓ માટે, સમાન ચાર્જ અલગ સંભવિત પેદા કરશે. પરંતુ φ હંમેશા q ના પ્રમાણસર હોય છે:

φ=Cq

ગુણાંક C ને ઇલેક્ટ્રિકલ કેપેસીટન્સ કહેવામાં આવે છે.જો આપણે ઘણા વાહક (સામાન્ય રીતે બે) ની સિસ્ટમ વિશે વાત કરી રહ્યા છીએ, તો જ્યારે એક વાહક (પ્લેટ) પર ચાર્જ આપવામાં આવે છે, ત્યારે સંભવિત તફાવત અથવા વોલ્ટેજ U થાય છે:

U=Cq, તેથી С=U/q

કેપેસિટીન્સને ચાર્જના સંભવિત તફાવતના ગુણોત્તર તરીકે વ્યાખ્યાયિત કરી શકાય છે જેના કારણે તે થાય છે. કેપેસીટન્સ માટેનું SI એકમ ફરાડ છે (તેઓ ફરાડ કહેતા હતા). 1 F \u003d 1 V / 1 C. બીજા શબ્દોમાં કહીએ તો, સિસ્ટમમાં 1 ફેરાડની ક્ષમતા હોય છે, જેમાં, જ્યારે 1 કૂલમ્બનો ચાર્જ આપવામાં આવે છે, ત્યારે 1 વોલ્ટનો સંભવિત તફાવત ઊભો થાય છે. 1 ફરાડ એ ખૂબ મોટી કિંમત છે. વ્યવહારમાં, અપૂર્ણાંક મૂલ્યો મોટાભાગે ઉપયોગમાં લેવાય છે - પીકોફારાડ, નેનોફારાડ, માઇક્રોફારાડ.

વ્યવહારમાં, આવા જોડાણથી બેટરી મેળવવાનું શક્ય બને છે જે એક કોષ કરતાં ડાઇલેક્ટ્રિકના વધુ બ્રેકડાઉન વોલ્ટેજનો સામનો કરી શકે છે.

કેપેસિટર્સની કેપેસિટેન્સની ગણતરી

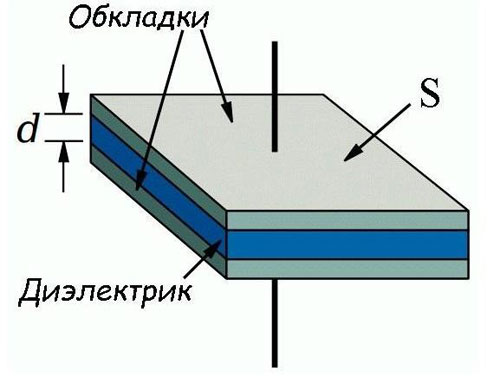

વ્યવહારમાં, સામાન્યકૃત ઇલેક્ટ્રિક કેપેસીટન્સવાળા તત્વો તરીકે, મોટેભાગે ઉપયોગમાં લેવાય છે કેપેસિટર્સ, બે સપાટ વાહક (પ્લેટ) નો સમાવેશ થાય છે, જે ડાઇલેક્ટ્રિક દ્વારા અલગ પડે છે. આવા કેપેસિટરની ઇલેક્ટ્રિક કેપેસિટેન્સની ગણતરી માટેનું સૂત્ર આના જેવું લાગે છે:

C=(S/d)*ε*ε0

ક્યાં:

- સી - ક્ષમતા, એફ;

- S એ ફેસિંગનો વિસ્તાર છે, sq.m;

- d એ પ્લેટો વચ્ચેનું અંતર છે, m;

- ε0 - વિદ્યુત સ્થિર, સ્થિર, 8.854 * 10−12 f/m;

- ε એ ડાઇલેક્ટ્રિકની વિદ્યુત પરવાનગી છે, એક પરિમાણહીન જથ્થો.

આના પરથી તે સમજવું સરળ છે કે કેપેસીટન્સ પ્લેટોના ક્ષેત્રફળના સીધા પ્રમાણસર છે અને કંડક્ટર વચ્ચેના અંતરના વિપરિત પ્રમાણસર છે. ઉપરાંત, પ્લેટોને અલગ કરતી સામગ્રી દ્વારા ક્ષમતાને અસર થાય છે.

કેપેસીટન્સ નક્કી કરતા જથ્થાઓ ચાર્જ સંગ્રહિત કરવાની કેપેસિટરની ક્ષમતાને કેવી રીતે અસર કરે છે તે સમજવા માટે, તમે સૌથી વધુ સંભવિત કેપેસીટન્સ સાથે કેપેસિટર બનાવવા માટે વિચાર પ્રયોગ કરી શકો છો.

- તમે પ્લેટોનો વિસ્તાર વધારવાનો પ્રયાસ કરી શકો છો. આ ઉપકરણના પરિમાણો અને વજનમાં તીવ્ર વધારો તરફ દોરી જશે. તેમને અલગ કરતા ડાઇલેક્ટ્રિક વડે અસ્તરનું કદ ઘટાડવા માટે, તેઓને વળેલું છે (એક ટ્યુબ, ફ્લેટ બ્રિકેટ વગેરેમાં).

- બીજી રીત પ્લેટો વચ્ચેનું અંતર ઘટાડવાનું છે. કંડક્ટરને ખૂબ નજીક રાખવું હંમેશા શક્ય નથી, કારણ કે ડાઇલેક્ટ્રિક સ્તર પ્લેટો વચ્ચેના ચોક્કસ સંભવિત તફાવતને ટકી શકે છે. જાડાઈ જેટલી નાની, ઇન્સ્યુલેટીંગ ગેપની ડાઇલેક્ટ્રિક તાકાત ઓછી. જો તમે આ માર્ગ અપનાવો છો, તો એવો સમય આવશે જ્યારે આવા કેપેસિટરનો વ્યવહારુ ઉપયોગ અર્થહીન બની જશે - તે માત્ર અત્યંત નીચા વોલ્ટેજ પર જ કામ કરી શકે છે.

- ડાઇલેક્ટ્રિકની વિદ્યુત અભેદ્યતામાં વધારો. આ પાથ આ ક્ષણે અસ્તિત્વમાં છે તે ઉત્પાદન તકનીકોના વિકાસ પર આધારિત છે. ઇન્સ્યુલેટીંગ સામગ્રીમાં માત્ર ઉચ્ચ અભેદ્યતા મૂલ્ય હોવું જોઈએ નહીં, પરંતુ સારા ડાઇલેક્ટ્રિક ગુણધર્મો પણ હોવા જોઈએ, અને તેના પરિમાણોને આવશ્યક આવર્તન શ્રેણીમાં જાળવવા જોઈએ (કેપેસિટર જે આવર્તન પર કાર્ય કરે છે તેમાં વધારો સાથે, ડાઇલેક્ટ્રિકની લાક્ષણિકતાઓમાં ઘટાડો થાય છે).

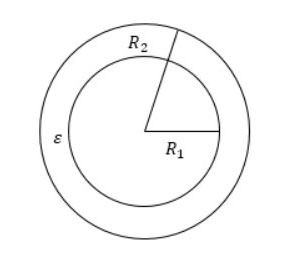

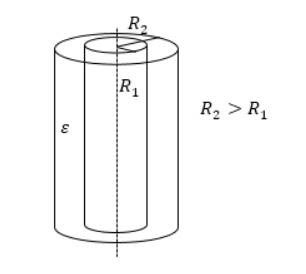

કેટલાક વિશિષ્ટ અથવા સંશોધન સ્થાપનો ગોળાકાર અથવા નળાકાર કેપેસિટરનો ઉપયોગ કરી શકે છે.

ગોળાકાર કેપેસિટરની કેપેસિટેન્સની ગણતરી સૂત્ર દ્વારા કરી શકાય છે

C=4*π*ε*ε0 *R1R2/(R2-R1)

જ્યાં R એ ગોળાની ત્રિજ્યા છે, અને π=3.14.

નળાકાર કેપેસિટર માટે, કેપેસિટેન્સની ગણતરી આ રીતે કરવામાં આવે છે:

C=2*π*ε*ε0 *l/ln(R2/R1)

l એ સિલિન્ડરોની ઊંચાઈ છે, અને R1 અને R2 તેમની ત્રિજ્યા છે.

મૂળભૂત રીતે, બંને સૂત્રો ફ્લેટ કેપેસિટર માટેના સૂત્રથી અલગ નથી. કેપેસીટન્સ હંમેશા પ્લેટોના રેખીય પરિમાણો, તેમની વચ્ચેનું અંતર અને ડાઇલેક્ટ્રિકના ગુણધર્મો દ્વારા નક્કી કરવામાં આવે છે.

કેપેસિટર્સની શ્રેણી અને સમાંતર જોડાણ

કેપેસિટર્સ કનેક્ટ કરી શકાય છે શ્રેણીમાં અથવા સમાંતરમાં, નવી લાક્ષણિકતાઓ સાથે સમૂહ મેળવવો.

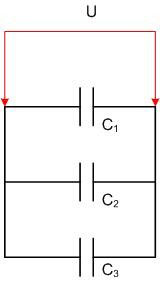

સમાંતર જોડાણ

જો તમે કેપેસિટર્સને સમાંતરમાં કનેક્ટ કરો છો, તો પરિણામી બેટરીની કુલ ક્ષમતા તેના ઘટકોની તમામ ક્ષમતાઓના સરવાળા જેટલી છે. જો બેટરીમાં સમાન ડિઝાઇનના કેપેસિટર હોય, તો આને પ્લેટોના ક્ષેત્રના ઉમેરા તરીકે ગણી શકાય. આ કિસ્સામાં, બેટરીના દરેક કોષ પરનો વોલ્ટેજ સમાન હશે, અને ચાર્જમાં વધારો થશે. સમાંતરમાં જોડાયેલા ત્રણ કેપેસિટર્સ માટે:

- U=U1=યુ2=યુ3;

- q=q1+q2+q3;

- C=C1+C2+C3.

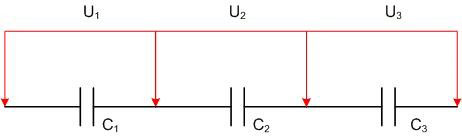

સીરીયલ કનેક્શન

જ્યારે શ્રેણીમાં જોડાયેલ હોય, ત્યારે દરેક કેપેસીટન્સનો ચાર્જ સમાન હશે:

q1=q2=q3=q

કુલ વોલ્ટેજ પ્રમાણસર વિતરિત કરવામાં આવે છે કેપેસિટર્સની ક્ષમતા:

- યુ1=q/C1;

- યુ2=q/C2;

- યુ3= q/C3.

જો બધા કેપેસિટર્સ સમાન હોય, તો દરેકમાં સમાન વોલ્ટેજ ડ્રોપ થાય છે. કુલ ક્ષમતા આ રીતે જોવા મળે છે:

С=q/( યુ1+યુ2+યુ3), તેથી 1/С=( U1+યુ2+યુ3)/q=1/C1+1/એસ2+1/એસ3.

ટેકનોલોજીમાં કેપેસિટરનો ઉપયોગ

વિદ્યુત ઊર્જા સંગ્રહ ઉપકરણો તરીકે કેપેસિટરનો ઉપયોગ કરવો તે તાર્કિક છે. આ ક્ષમતામાં, તેઓ નાની સંગ્રહિત ઊર્જાને કારણે ઇલેક્ટ્રોકેમિકલ સ્ત્રોતો (ગેલ્વેનિક બેટરી, કેપેસિટર્સ) સાથે સ્પર્ધા કરી શકતા નથી અને ડાઇલેક્ટ્રિક દ્વારા ચાર્જ લીકેજને કારણે ઝડપથી સ્વ-ડિસ્ચાર્જ થાય છે.પરંતુ લાંબા સમય સુધી ઊર્જા એકઠા કરવાની અને પછી લગભગ તરત જ તેને દૂર કરવાની તેમની ક્ષમતાનો વ્યાપકપણે ઉપયોગ થાય છે. આ ગુણધર્મનો ઉપયોગ ફોટોગ્રાફી માટે ફ્લેશ લેમ્પમાં અથવા લેસરોના ઉત્તેજના માટે લેમ્પમાં થાય છે.

રેડિયો એન્જિનિયરિંગ અને ઇલેક્ટ્રોનિક્સમાં કેપેસિટરનો વ્યાપકપણે ઉપયોગ થાય છે. સર્કિટ્સના ફ્રીક્વન્સી-સેટિંગ તત્વોમાંના એક તરીકે રેઝોનન્ટ સર્કિટના ભાગ રૂપે કેપેસિટીન્સનો ઉપયોગ થાય છે (બીજું તત્વ ઇન્ડક્ટન્સ છે). તે વેરિયેબલ ઘટકમાં વિલંબ કર્યા વિના ડાયરેક્ટ કરંટ પસાર ન કરવા માટે કેપેસિટર્સની ક્ષમતાનો પણ ઉપયોગ કરે છે. એક સ્ટેજના ડીસી મોડ્સના પ્રભાવને બીજા સ્ટેજ પર બાકાત રાખવા માટે એમ્પ્લીફાઇંગ સ્ટેજને અલગ કરવા માટે આવી એપ્લિકેશન સામાન્ય છે. મોટા કેપેસિટરનો ઉપયોગ પાવર સપ્લાયમાં સ્મૂથિંગ ફિલ્ટર તરીકે થાય છે. કેપેસિટરના અન્ય એપ્લીકેશનો પણ મોટી સંખ્યામાં છે જ્યાં તેમની મિલકતો ઉપયોગી છે.

કેટલાક વ્યવહારુ કેપેસિટર ડિઝાઇન

વ્યવહારમાં, ફ્લેટ કેપેસિટરની વિવિધ ડિઝાઇનનો ઉપયોગ થાય છે. ઉપકરણની ડિઝાઇન તેની લાક્ષણિકતાઓ અને અવકાશ નક્કી કરે છે.

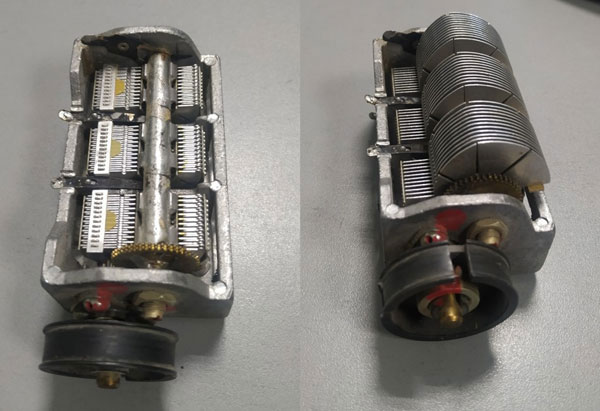

ચલ કેપેસિટર

એક સામાન્ય પ્રકારનું વેરિયેબલ કેપેસિટર (VPC) હવા દ્વારા અલગ કરાયેલ જંગમ અને સ્થિર પ્લેટોના બ્લોક અથવા ઘન ઇન્સ્યુલેટર ધરાવે છે. જંગમ પ્લેટો અક્ષની આસપાસ ફરે છે, ઓવરલેપ એરિયામાં વધારો અથવા ઘટાડો કરે છે. જ્યારે મૂવિંગ બ્લોક દૂર કરવામાં આવે છે, ત્યારે ઇન્ટરઇલેક્ટ્રોડ ગેપ યથાવત રહે છે, પરંતુ પ્લેટો વચ્ચેનું સરેરાશ અંતર પણ વધે છે. ઇન્સ્યુલેટરનું ડાઇલેક્ટ્રિક સ્થિરાંક પણ યથાવત રહે છે. પ્લેટોના ક્ષેત્રફળ અને તેમની વચ્ચેના સરેરાશ અંતરને બદલીને ક્ષમતાને નિયંત્રિત કરવામાં આવે છે.

ઓક્સાઇડ કેપેસિટર

અગાઉ, આવા કેપેસિટરને ઇલેક્ટ્રોલિટીક કહેવામાં આવતું હતું. તેમાં ઇલેક્ટ્રોલાઇટ વડે ગર્ભિત પેપર ડાઇલેક્ટ્રિક દ્વારા અલગ કરાયેલા વરખની બે પટ્ટીઓ હોય છે. પ્રથમ સ્ટ્રીપ એક પ્લેટ તરીકે સેવા આપે છે, બીજી પ્લેટ ઇલેક્ટ્રોલાઇટ તરીકે સેવા આપે છે. ડાઇલેક્ટ્રિક એ ધાતુની એક પટ્ટી પર ઓક્સાઇડનું પાતળું પડ છે અને બીજી પટ્ટી વર્તમાન કલેક્ટર તરીકે કામ કરે છે.

હકીકત એ છે કે ઓક્સાઇડ સ્તર ખૂબ જ પાતળું છે, અને ઇલેક્ટ્રોલાઇટ તેને નજીકથી જોડે છે, મધ્યમ કદ સાથે પૂરતી મોટી ક્ષમતાઓ મેળવવાનું શક્ય બન્યું. આની કિંમત ઓછી ઓપરેટિંગ વોલ્ટેજ હતી - ઓક્સાઇડ સ્તરમાં ઉચ્ચ વિદ્યુત શક્તિ નથી. ઓપરેટિંગ વોલ્ટેજમાં વધારો સાથે, કેપેસિટરના પરિમાણોમાં નોંધપાત્ર વધારો કરવો જરૂરી છે.

બીજી સમસ્યા એ છે કે ઓક્સાઇડમાં એકતરફી વાહકતા હોય છે, તેથી આવા કન્ટેનરનો ઉપયોગ માત્ર ધ્રુવીયતા સાથે ડીસી સર્કિટમાં થાય છે.

આયોનિસ્ટર

ઉપર બતાવ્યા પ્રમાણે, વધતી પરંપરાગત પદ્ધતિઓ કેપેસિટર્સ કુદરતી મર્યાદાઓ છે. તેથી, વાસ્તવિક સફળતા એ ionistors ની રચના હતી.

જો કે આ ઉપકરણને કેપેસિટર અને બેટરી વચ્ચેની મધ્યવર્તી કડી માનવામાં આવે છે, સારમાં તે હજુ પણ કેપેસિટર છે.

ડબલ વિદ્યુત સ્તરના ઉપયોગને કારણે પ્લેટો વચ્ચેનું અંતર ભારે ઘટાડો થાય છે. પ્લેટો વિરોધી ચાર્જ સાથે આયનોના સ્તરો છે. ફીણવાળી છિદ્રાળુ સામગ્રીને લીધે પ્લેટોના ક્ષેત્રફળમાં તીવ્ર વધારો કરવાનું શક્ય બન્યું. પરિણામે, સેંકડો ફેરાડ્સ સુધીની ક્ષમતા સાથે સુપરકેપેસિટર્સ મેળવવાનું શક્ય છે.આવા ઉપકરણોનો જન્મજાત રોગ ઓછો ઓપરેટિંગ વોલ્ટેજ છે (સામાન્ય રીતે 10 વોલ્ટની અંદર).

તકનીકીનો વિકાસ સ્થિર નથી - ઘણા વિસ્તારોમાંથી લેમ્પ્સ દ્વિધ્રુવી ટ્રાંઝિસ્ટર દ્વારા વિસ્થાપિત થાય છે, તે બદલામાં, યુનિપોલર ટ્રાયોડ્સ દ્વારા બદલવામાં આવે છે. સર્કિટ ડિઝાઇન કરતી વખતે, તેઓ શક્ય હોય ત્યાં ઇન્ડક્ટન્સથી છુટકારો મેળવવાનો પ્રયાસ કરે છે. અને કેપેસિટરોએ બીજી સદી સુધી તેમની સ્થિતિ ગુમાવી નથી, લેડેન જારની શોધ પછી તેમની ડિઝાઇન મૂળભૂત રીતે બદલાઈ નથી, અને તેમની કારકિર્દી સમાપ્ત કરવાની કોઈ સંભાવના નથી.

સમાન લેખો: